Combinatorial Logic#

The truth tables shown below describes the operation of the AND, OR, and INVERTER logic gates. These are examples of combinatorial logic functions since the outputs are only dependent on the present state of the inputs.

Inputs |

Outputs |

||

|---|---|---|---|

A | B |

AND |

OR |

INV A |

0 | 0 |

0 |

0 |

1 |

0 | 1 |

0 |

1 |

1 |

1 | 0 |

0 |

1 |

0 |

1 | 1 |

1 |

1 |

0 |

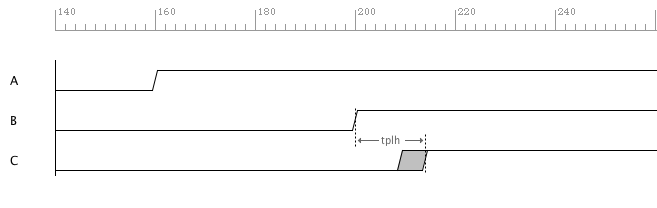

Propagation Delay#

The propagation delay of the logic gate specifies how long it takes the output to change after the inputs changed. This delay is defined the manufacturer of the part and can actually be specified as two delays. \(t_{plh}\) indicates the delay when the output is changing from a 0 to 1, and \(t_{phl}\) indicates the delay when the output is changing from a 1 to 0.

\(t_{plh}\) Low to High Output Propagation Delay

\(t_{phl}\) High to Low Output Propagation Delay

Example Problem.

- Given.

\(t_{plh}\) = 9ns minimum and 14ns maximum

\(t_{phl}\) = 8ns minimum and 13ns maximum

A = 1 and B = 0 and C = 0 @ t = 100ns

A = 1 and B = 1 @ t = 200ns

At what time will the AND gate output C change to a 1?

Answer: \(t_{plhmax} + 200ns = 14ns + 200ns = 214ns\)

Considering minimum and maximum delays are specified, the output could actually change between 200ns + 9ns and 200ns +14ns. This is called the delay margin.

Propagation Delay of Combinatorial AND Gate.#

1if "new.tim" != taApp.getFileName():

2 taApp.fileNew("TimingDiagram")

3

4td = taApp.getTimingDiagram()

5td.startScript()

6

7ain = td.add_digital_signal("A","L")

8bin = td.add_digital_signal("B","L")

9cout = td.add_digital_signal("C","L")

10

11a_e1 = td.add_edge(ain,160,"H")

12b_e1 = td.add_edge(bin,200,"H")

13c_e1 = td.add_edge(cout,200,"H")

14

15tplh = td.add_part_delay("tplh", 9, 11, 14, "AND Gate Prop Delay")

16td.add_delay(tplh,b_e1,c_e1)

17

18td.stopScript()