Script Examples#

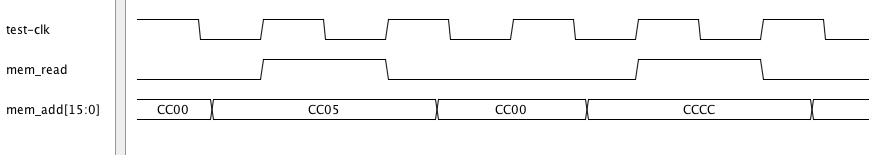

Drawing a Timing Diagram#

The script draw_diagram.py is shown below

1from ta_py_lib.ta.app import *

2from ta_py_lib.td.logic import *

3from ta_py_lib.td.commands import *

4

5td = new_timing_diagram(taApp)

6start_script(td)

7

8dclock = add_digital_clock(td, "test-clk", "H", 20.0e6)

9dsignal = add_digital_signal(td, "mem_read", "L")

10dbus = add_digital_bus(td, "mem_add[15:0]", "CC00", "Hex")

11

12add_pulse(dsignal, 50.0, 100.0, "H")

13add_pulse(dbus, 30.0, 120.0, "CC05")

14

15add_edge(dsignal, 200.0, "H")

16add_edge(dsignal, 250.0, "L")

17

18add_edge(dbus, 180.0, "CCCC")

19add_edge(dbus, 270.0, "CD00")

20

21stop_script(td)

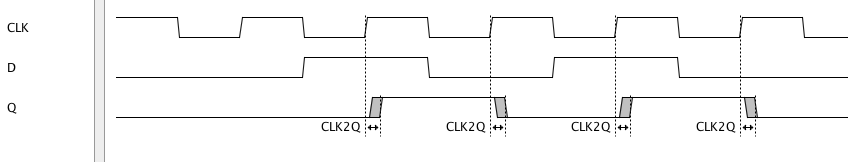

Creating a D Flip Flop#

The script dff.py is shown below

1from ta_py_lib.ta.app import *

2from ta_py_lib.td.logic import *

3from ta_py_lib.td.commands import *

4

5td = new_timing_diagram(taApp)

6start_script(td)

7

8clk = add_digital_clock(td, "CLK","H",20.0e6)

9sigD = add_digital_signal(td, "D","L")

10sigQ = add_digital_signal(td, "Q","L")

11

12add_pulse(sigD, 75.0, 125.0, "H")

13add_edge(sigD, 175.0, "H")

14add_edge(sigD, 225.0, "L")

15

16dly_min = 2

17dly_typ = 4

18dly_max = 6

19clk2q_dly = add_part_delay(td, "CLK2Q", dly_min, dly_typ, dly_max, "DFF Clock to Q Output Delay")

20clk_edge_list = get_edge_list(clk)

21

22ls = "L"

23for clk_edge in clk_edge_list:

24 if get_next_state(clk_edge) == "H":

25 et = get_pt2_min(clk_edge)

26 ns = get_state_at_time(sigD, et)

27 #print "edge time %d next state %s" % (et,ns)

28 if ((ns != ls) and (et + dly_min > get_last_edge_pt2(sigQ))):

29 sigQ_edge = add_edge(sigQ, et, ns)

30 add_delay(td, clk2q_dly,clk_edge,sigQ_edge)

31 ls = ns

32

33stop_script(td)

Dumping Signal Values#

The script dump_edges.py is shown below

1from org.dmad.ta import DigitalClock

2from ta_py_lib.ta.app import *

3from ta_py_lib.td.logic import *

4from ta_py_lib.td.commands import *

5from ta_py_lib.td.utils import *

6

7td = get_timing_diagram(taApp)

8start_script(td)

9

10out_file = set_output_file("dump_edges.txt")

11

12signal_list = get_signal_list(td)

13

14clock_signal = None

15for signal in signal_list:

16 if isinstance(signal, DigitalClock):

17 clock_signal = signal

18 else:

19 out_file.write("%s " % (get_name(signal)))

20

21out_file.write("\n")

22

23for clock_edge in get_edge_list(clock_signal):

24 if get_next_state(clock_edge) == "H":

25 edge_time = get_pt2_min(clock_edge)

26 for sig in signal_list:

27 if sig != clock_signal:

28 out_file.write("%s " % (get_state_at_time(sig, edge_time)))

29 out_file.write("\n")

30

31out_file.close()

32

33stop_script(td)

An example output from dump_edges.py

1D Q D_diff mem_read mem_add[15:0]

2H L L H L CC00

3H L L H H CC05

4H H L L L CC05

5H L H H L CC00

6H H L L H CCCC

7H L H H L CCCC

8H L L H L CD00

Generating VHDL Test Vectors#

The script vhdl_test_vectors.py is shown below

1from org.dmad.ta import DigitalSignal

2from org.dmad.ta import DigitalBus

3from org.dmad.ta import DigitalClock

4

5from ta_py_lib.ta.app import *

6from ta_py_lib.td.logic import *

7from ta_py_lib.td.commands import *

8from ta_py_lib.td.utils import *

9

10out_file = set_output_file("vhdl_test_vectors.txt")

11td = get_timing_diagram(taApp)

12

13start_script(td)

14

15ts = get_time_scale(td)

16ts_text = get_time_scale_text(ts)

17signals = get_signal_list(td)

18

19for sig in signals:

20 i = 0

21

22 out_file.write("%s <= " % (get_name(sig)))

23

24 for edge in get_edge_list(sig):

25 if isinstance(sig, DigitalSignal) or isinstance(sig, DigitalClock):

26 line = "'%s'" % (get_next_state(edge))

27 if i != 0:

28 line = " %s after %s %s" % (line, edge.getPt2Min() / 1000, ts_text)

29 elif isinstance(sig, DigitalBus):

30 state_format = {

31 "Hex": "X\"",

32 "Bin": "\""

33 }

34

35 sStart = state_format[get_state_format(sig)]

36

37 line = "%s%s\"" % (sStart, get_next_state(edge))

38 if i != 0:

39 line = " %s after %s %s" % (line, edge.getPt2Min() / 1000, ts_text)

40

41 if ( i == len(get_edge_list(sig))-1):

42 out_file.write("%s;\n\n" % (line))

43 else:

44 out_file.write("%s,\n" % (line))

45

46 i += 1

47out_file.close()

48stop_script(td)

An example output from vhdl_test_vectors.py

1ADD[15:0] <= X"Z",

2 X"FFC0" after 27.0 ns,

3 X"Z" after 82.0 ns,

4 X"DC00" after 1027.0 ns,

5 X"Z" after 1082.0 ns;

6

7CS <= 'H',

8 'L' after 34.0 ns,

9 'H' after 82.0 ns,

10 'L' after 1034.0 ns,

11 'H' after 1082.0 ns;

12

13DATA[7:0] <= X"Z",

14 X"55" after 49.0 ns,

15 X"Z" after 82.0 ns,

16 X"AA" after 1041.0 ns,

17 X"Z" after 1082.0 ns;

Generating SPICE PWL Test Vectors#

The script spice_pwl_test_vectors.py is shown below

1from org.dmad.ta import DigitalBus

2from ta_py_lib.ta.app import *

3from ta_py_lib.td.logic import *

4from ta_py_lib.td.commands import *

5from ta_py_lib.td.utils import *

6

7td = get_timing_diagram(taApp)

8start_script(td)

9

10ts = get_time_scale(td)

11out_file = set_output_file('spice_pwl_test_vectors_py.txt')

12

13sig_list = get_signal_list(td)

14for sig in sig_list:

15 if not isinstance(sig, DigitalBus):

16 out_file.write("%s N1 N2 PWL (\n" % (get_name(sig)))

17 out_file.write(" 0.0 %s\n" % (get_voltage(get_start_state(sig))))

18

19 ed_list = get_edge_list(sig)

20 i = 0

21 for ed in ed_list:

22 if i > 0:

23 ls_voltage = get_voltage(get_last_state(ed))

24 ns_voltage = get_voltage(get_next_state(ed))

25 out_file.write(" %f%s %s\n" % (get_pt1_min(ed) / 1000.0, get_ts_text(ts), ls_voltage))

26 out_file.write(" %f%s %s\n" % (get_pt3_min(ed) / 1000.0, get_ts_text(ts), ns_voltage))

27 i += 1

28 out_file.write(" %f%s %s\n" % (get_end_time(td), get_ts_text(ts), ns_voltage))

29 out_file.write(" )\n")

30 else:

31 num_bits = get_num_bits(sig)

32 state_format = get_state_format(sig)

33

34 ls_bit = get_ls_bit(get_name(sig))

35 ms_bit = get_ms_bit(get_name(sig))

36

37 for i in range(ls_bit,ms_bit+1):

38 start_state = get_start_state(sig);

39 if (state_format != "Bin"):

40 start_state = convert_format(start_state,state_format,"Bin",num_bits)

41

42 bus_name = get_name(sig)

43 bus_name = bus_name[0:bus_name.find("[")]

44 out_file.write("%s[%d] N1 N2 PWL (\n" % (bus_name,i))

45

46 if (start_state == "Z"):

47 ss_voltage = get_voltage("Z")

48 else:

49 ss_voltage = get_voltage(start_state[i])

50

51 out_file.write(" 0.0 %s\n" % (ss_voltage))

52

53 ed_list = get_edge_list(sig)

54 j = 0

55 for ed in ed_list:

56 if (j > 0):

57 last_state = get_last_state(ed)

58 if (state_format != "Bin"):

59 last_state = convert_format(last_state,state_format,"Bin",num_bits)

60 if (last_state == "Z"):

61 ls_voltage = get_voltage("Z")

62 else:

63 ls_voltage = get_voltage(last_state[ms_bit-i])

64

65 next_state = get_next_state(ed)

66 if (state_format != "Bin"):

67 next_state = convert_format(next_state,state_format,"Bin",num_bits)

68 if (next_state == "Z"):

69 ns_voltage = get_voltage("Z")

70 else:

71 ns_voltage = get_voltage(next_state[ms_bit-i])

72

73 out_file.write(" %f%s %s\n" % (get_pt1_min(ed) / 1000, get_ts_text(ts), ls_voltage))

74 out_file.write(" %f%s %s\n" % (get_pt3_min(ed) / 1000, get_ts_text(ts), ns_voltage))

75 j += 1

76 end_voltage = ns_voltage

77 out_file.write(" %f%s %s\n" % (get_end_time(td), get_ts_text(ts), end_voltage))

78 out_file.write(" )\n")

79

80out_file.close()

81stop_script(td)

An example output from spice_pwl_test_vectors.py

1ADD[1] N1 N2 PWL (

2 0.0 2.5

3 26.500000e-9 2.5

4 27.500000e-9 0.0

5 81.500000e-9 0.0

6 82.500000e-9 2.5

7 1026.500000e-9 2.5

8 1027.500000e-9 0.0

9 1081.500000e-9 0.0

10 1082.500000e-9 2.5

11 1120.000000e-9 2.5

12 )

13ADD[2] N1 N2 PWL (

14 0.0 2.5

15 26.500000e-9 2.5

16 27.500000e-9 0.0

17 81.500000e-9 0.0

18 82.500000e-9 2.5

19 1026.500000e-9 2.5

20 1027.500000e-9 0.0

21 1081.500000e-9 0.0

22 1082.500000e-9 2.5

23 1120.000000e-9 2.5

24 )

25ADD[3] N1 N2 PWL (

26 0.0 2.5

27 26.500000e-9 2.5

28 27.500000e-9 0.0

29 81.500000e-9 0.0

30 82.500000e-9 2.5

31 1026.500000e-9 2.5

32 1027.500000e-9 0.0

33 1081.500000e-9 0.0

34 1082.500000e-9 2.5

35 1120.000000e-9 2.5

36 )